NEXTGenIO: the next exciting stage begins!

24 November 2016

NEXTGenIO was one of several EC-funded exascale projects that we started work on last year. Here’s what’s been happening since it launched.

The goal of NEXTGenIO is to develop a new HPC platform around Intel’s 3D XPoint™ non-volatile memory.

“Platform” in our case does not only mean the hardware, although that is of course a big part of it, but also the entire software stack that sits on top of the hardware. Our challenge is to think of how we believe this new memory technology should be used both in current and future HPC systems to alleviate some of the I/O performance bottlenecks that affect so many applications today. The past months have therefore been spent teasing out the requirements based on a set of usage scenarios.

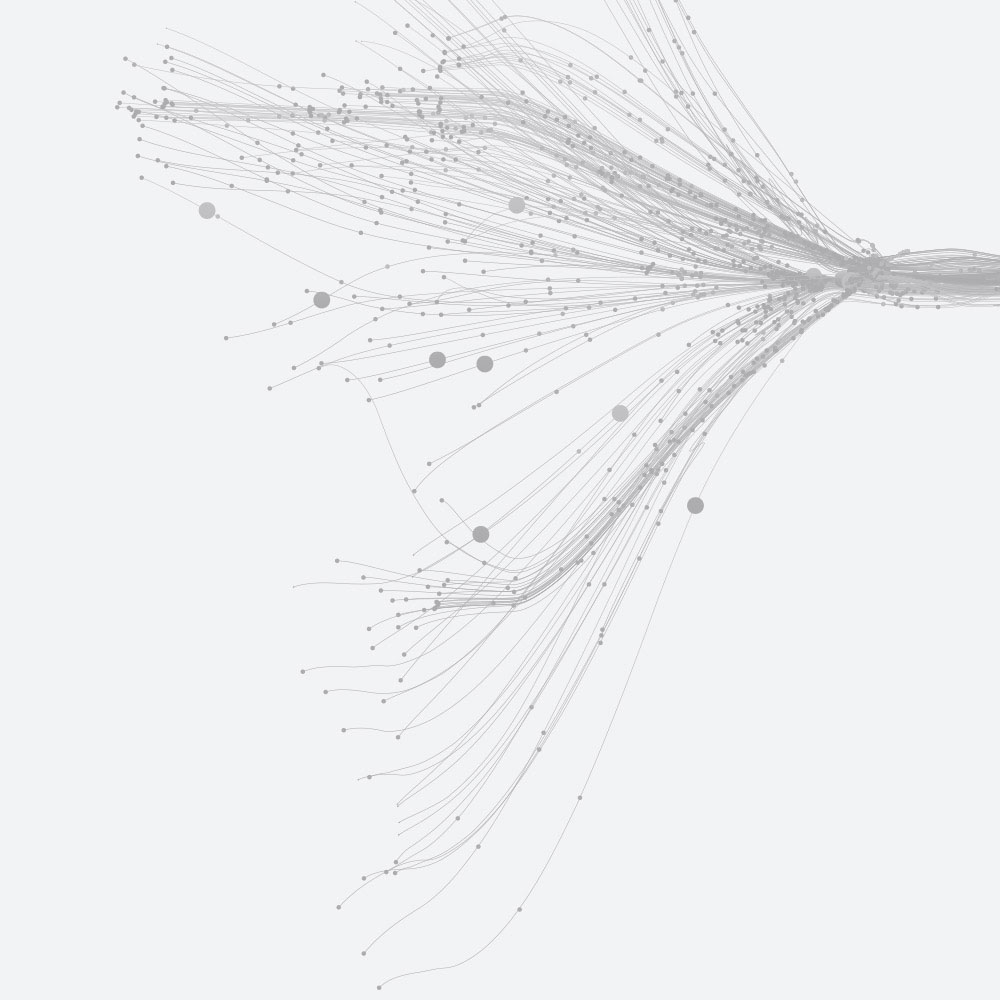

One of these scenarios is an operational run of IFS, the main forecasting model used at the European Centre for Medium Range Weather Forecast (ECMWF). Collectively, the forecast writes 7 million fields in a one-hour operational window. As the operational timetable is tight, even small gains in runtime have a big impact on the schedule. Within NEXTGenIO, the IFS output server will be adapted to exploit the non-volatile memory to avoid writing fields to disk within the time-critical window.

Another usage scenario is that of bioinformatics computations, a relatively new field for HPC. Bioinformatics applications are often characterised by a workflow where one application may read data then produce output, which is in turn consumed by another application. Reading and writing data to be passed between applications takes a long time, so reducing this cost is important.

One key requirement, and an important driver for the architecture, is the need for legacy applications to “just run” on the new platform without requiring anything more than a recompilation.

Implementation

We have now completed our designs of the hardware, the systemware and the data architectures for NEXTGenIO, and the implementation phase – the exciting part – is under way.

In July, the consortium had the chance to visit the Fujitsu factory in Augsburg where the NEXTGenIO hardware will be built. We were shown the motherboard design layout process (which is done by hand and takes 6 to 8 weeks) and all left with a real sense of progress being made!