A busy time at SC25!

12 November 2025

Supercomputing (SC), the HPC community's largest conference, is held annually over the course of a week in a major US city, this year St. Louis. The range of exhibitions, research papers, workshops, panels and community Birds of a Feather sessions means that there is something for everybody. This year is no exception, and I am involved in several activities throughout the week.

RISC-V at SC25

As chair of the RISC-V HPC SIG and a RISC-V ambassador, I have led workshops on RISC-V at both SC and ISC High Performance for the past few years. This year we have a packed RISC-V for HPC workshop programme, comprising the keynote talk from a Senior Fellow at Condor Computing who is responsible for their RISC-V product line, and then ten research papers exploring different aspects of the RISC-V ecosystem from CPUs to accelerators.

Paper presentation

As part of the workshop I will be presenting the paper Is RISC-V ready for High Performance Computing? An evaluation of the Sophon SG2044, in which we used NASA's Parallel Benchmark suite (NPB) to benchmark the SG2044. The RISC-V HPC community has relied on this CPU's predecessor, the 64-core SG2042, for a couple of years now and the SG2044 is an upgrade which, for example, provides full support for the vectorisation standard.

A couple of years ago we were the first to benchmark the SG2042 and found that whilst compute performance was fairly impressive, its major limitation was the memory subsystem. The SG2044 has significantly improved this aspect by increasing the number of memory controllers from 4 to 32, and also supporting DDR5, ultimately resulting in the CPU being between 1.5 and 4.9 times faster than the previous generation.

Panel

I am chairing a panel on the Thursday afternoon, 1:30pm to 3pm, entitled A Fully Open, Community-Driven HPC Ecosystem: A Credible Future or Chimera?. This session was inspired by the observation that RISC-V enables, really rather uniquely, openness at the hardware level. However, for a complete ecosystem one obviously also requires all the software side including the tooling, drivers and applications. Therefore it is potentially beneficial when talking about openness to view the entirety as a whole to understand how different parts might work together or any potential issues. From this we hope to better understand where the opportunities lie, and also challenges that must be solved by the community.

BoF session

I will be providing the RISC-V perspective to the CSx4HPC: Computational Storage for High Performance Computing Birds of a Feather (BoF) session, which is exploring how to handle exponentially growing data volumes. We are seeing a range of new hardware solutions, some based on RISC-V, emerge as promising technologies to address these issues.

Above: the RISC-V for HPC workshop at SC24.

Presenting compiler work for novel architectures

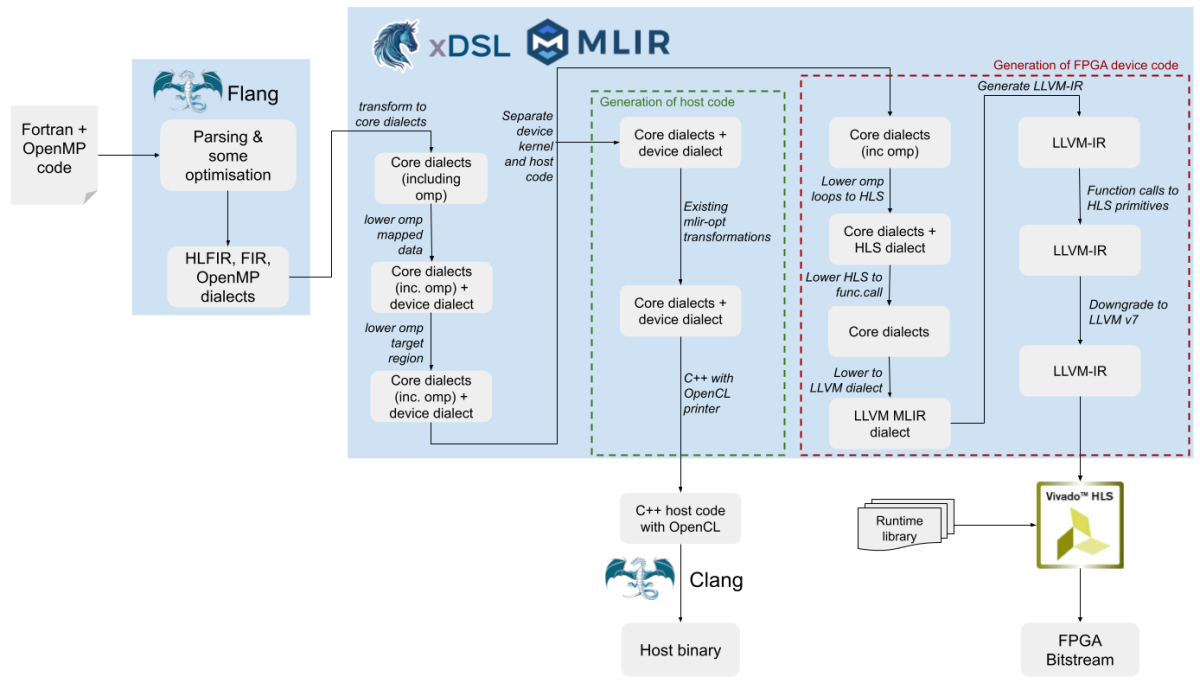

One of my PhD students, Gabriel Rodríguez Canal, and I have been exploring MLIR-based pipelines for FPGAs and AMD AI engines. Gabriel will present our paper An MLIR pipeline for offloading Fortran to FPGAs via OpenMP during the LLVM workshop on Monday morning. In this paper we focus on Fortran loops decorated with the OpenMP target pragma to offload these to the FPGA.

The purpose of the paper is two fold. Firstly to introduce the first (to the best of our knowledge) Fortran OpenMP flow for FPGAs, and secondly to act as a vehicle that demonstrates how the building blocks provided by MLIR can significantly lower the overhead in developing such compiler transformations. The second point is important, as this compiler pipeline builds on Gabriel's previous efforts during an internship with HPE (see the paper Fortran High-Level Synthesis: Reducing the barriers to accelerating HPC codes on FPGAs) to provide a connection between LLVM and AMD's High Level Synthesis (HLS) backend. It also builds on work he undertook on supporting stencils on FPGAs (see paper Stencil-HMLS: A multi-layered approach to the automatic optimisation of stencil codes on FPGA), which introduced an HLS MLIR dialect.

Secondly, Gabriel will present the paper Programmer productivity and performance on AMD's AI Engines: Offloading Fortran intrinsics via MLIR a case-study on Friday morning at the H2RC workshop, exploring once again leveraging MLIR to offload built-in Fortran intrinsics to AMD's AI Engines (AIEs). Not only do AMD's FPGAs, such as the Versal, optionally contain AIEs, but furthermore their Ryzen-AI CPU product line is also equipped with them. Leveraging some of my previous work, which in part connected intrinsics with the MLIR linalg dialect, the work that Gabriel will present involves a lowering of specific operations in the linalg dialect to the AIEs.

Above: Compiler flow developed in the LLVM workshop paper An MLIR pipeline for offloading Fortran to FPGAs via OpenMP, transforming Fortran with OpenMP decorated loops to FPGAs.

Talking about emerging architectures

I will be speaking at the Advanced Architecture Testbeds: Community Resources for Enhanced HPC Research BoF session about our successes on our Cerebras systems. The Cerebras contains an approximately 850,000 core Wafer-Scale Engine (WSE) and, whilst it was initially designed for AI/ML workloads, it has been demonstrated to work well for HPC and has the potential to transform memory bound problems into compute bound ones. I will highlight some of the activities that are going on in EPCC with the WSE and some of our successes.

Driving knowledge exchange for UK Digital Research Infrastructure (DRI)

I lead the Computational Abilities Knowledge Exchange (CAKE) UKRI/EPSRC funded network, and our objective is to drive knowledge exchange for the UK's DRI activities. SC is an important conference to this regard, and we will have plenty of CAKE/DRI representation on the SC exhibition show floor. We have collated a list of UK-wide SC activities going on throughout the week. Please drop by the EPCC, STFC and UK Universities booths to grab merchandise, find out more about the different DRI projects, and take part in a treasure hunt and win prizes!