The evolution of RISC architecture

11 April 2023

It is an exciting time for CPU development with the introduction of Apple’s ARM-based silicon and new RISC-V CPUs, even though the developer journey is currently a bit bumpy for the latter.

"[A] favorite theory of mine [is] that no occurrence is sole and solitary, but is merely a repetition of a thing which has happened before, and perhaps often." [1]

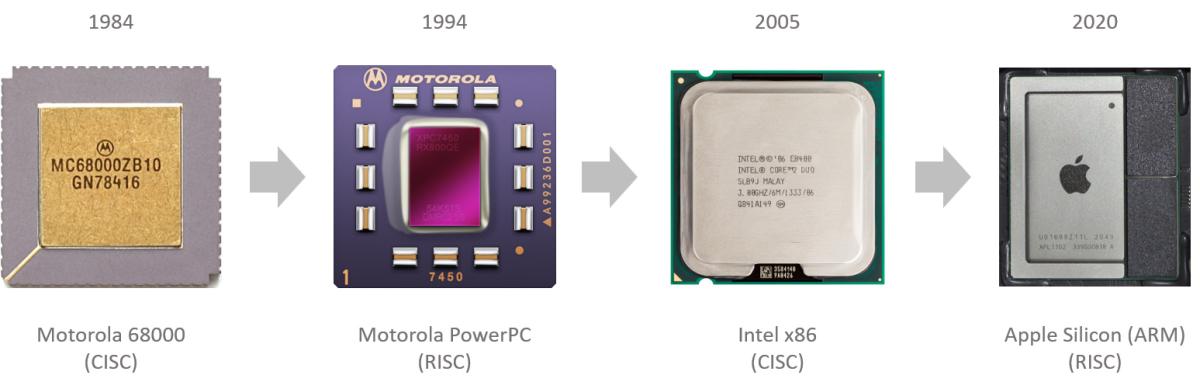

Mark Twain posits that there is a tendency for life to repeat itself. We can see evidence of this in the change of CPU architectures for the Apple Macintosh, as shown in Figure 1, where the original CISC (complex instruction set computer) Motorola 68000 was replaced by the RISC (reduced instruction set computer) Motorola PowerPC in 1994. This was, in turn, replaced by the CISC Intel x86 in 2005 and a return to RISC with the introduction of Apple Silicon, based on the ARM CPU, in 2020.

During the period between 2005 and 2020 the dominance of the Intel x86 as the CPU of choice for laptops, desktops, enterprise servers and HPC machines seemed unassailable, even though ARM had become dominant in mobile devices. Also, during this period, we saw the demise of competing RISC CPU architectures in the enterprise server and HPC domains, such as the Sun SPARC, MIPS and DEC Alpha, suggesting that, perhaps, CISC was the future of CPU architectures.

Figure 1 - Apple Macintosh CPU transition timeline.

However, for desktop and laptop machines, this assumption was challenged by Apple in 2020 with the introduction of the ARM-based Apple Silicon M1 system-on-chip (SoC). Which not only reduced the power consumption of the M1-based MacBook Pro versus the previous Intel-based version by around 90% but also increased runtime performance by approximately 75% [2]. Furthermore, the introduction of the Fujitsu ARM-based Supercomputer Fugaku, #1 on the Top500 list in November 2021 [3], further strengthened the challenge to the x86’s dominance as a CISC CPU architecture.

Although Fugaku was replaced by the x86-based Frontier system in the June 2022 Top500 list, it remains at #2 and suggests that the ARM will become a significant competitor to the x86, perhaps returning RISC as a dominant CPU architecture for high-performance machines. RISC CPU architectures are simpler to implement than CISC architectures, requiring a smaller area of silicon, with the associated reduced power consumption. This enables increased CPU clock frequency and a greater number of cores on the die, relative to CISC architectures, thereby increasing performance.

Whilst the leading SPARC, MIPS and Alpha RISC architectures have fallen by the wayside, leaving the ARM as the dominant RISC challenger to the x86, it isn’t the only RISC architecture gaining traction. RISC-V from UC Berkeley is the fifth version of the Berkeley RISC CPU architecture family and is currently generating a great deal of attention. It is generally accepted that this interest is due to the RISC-V instruction set architecture (ISA) being Open Source, allowing its unconstrained use. However, other CPU architectures are also Open Source, such as the SPARC (OpenSPARC [4]).

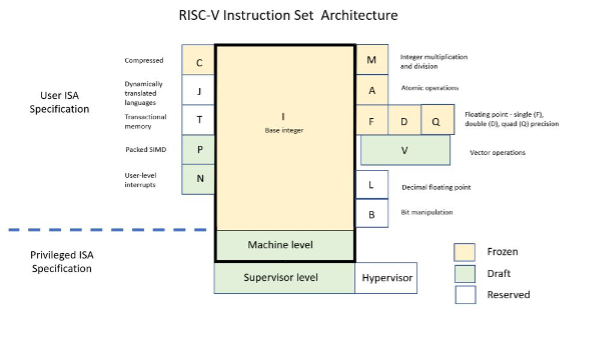

The key differentiator of RISC-V is that its ISA is modular. There are currently five ratified base ISAs: RVM0 (weak memory ordering), RV32I (base 32-bit integer), RV32E (base 32-bit integer with only 16 registers), RV64I (base 64-bit integer) and RV64E (base 64-bit integer with only 16 registers). As shown in Figure 2, a number of ISA extensions have also been defined [5], including support for single and double-precision floating point (‘F’ and ‘D’ respectively), compressed instructions (‘C’) and vector instructions (‘V’), that enable CPU designers to pick and choose the base ISA and extensions in order to provide specific functionality to meet their needs. For example, the RV32E base ISA only provides support for 16, rather than 32, registers which saves approximately 25% of the core’s silicon area with a corresponding power reduction [6]. This is beneficial in battery-powered embedded or edge devices that require very low power consumption. As these are individual extensions, compilers such as GCC and LLVM/Clang provide options to select arbitrary combinations of these as required. Not only does this modular approach provide hardware manufacturers with increased flexibility but also allows new extensions to be created and ratified without impacting the existing ISA specifications.

Figure 2: Base RISC-V ISA and extensions [7].

There are currently a number of embedded and low-end RISC-V CPUs / SoCs available, such as the 64-bit Allwinner D1 (based on the XuanTie C906) and the 64-bit quad-core SiFiveU740. There are also a large number of softcores, ranging from RV32E (eg PicoRV32) to RV64GC (eg XuanTie C910 and Andes X45) variants.

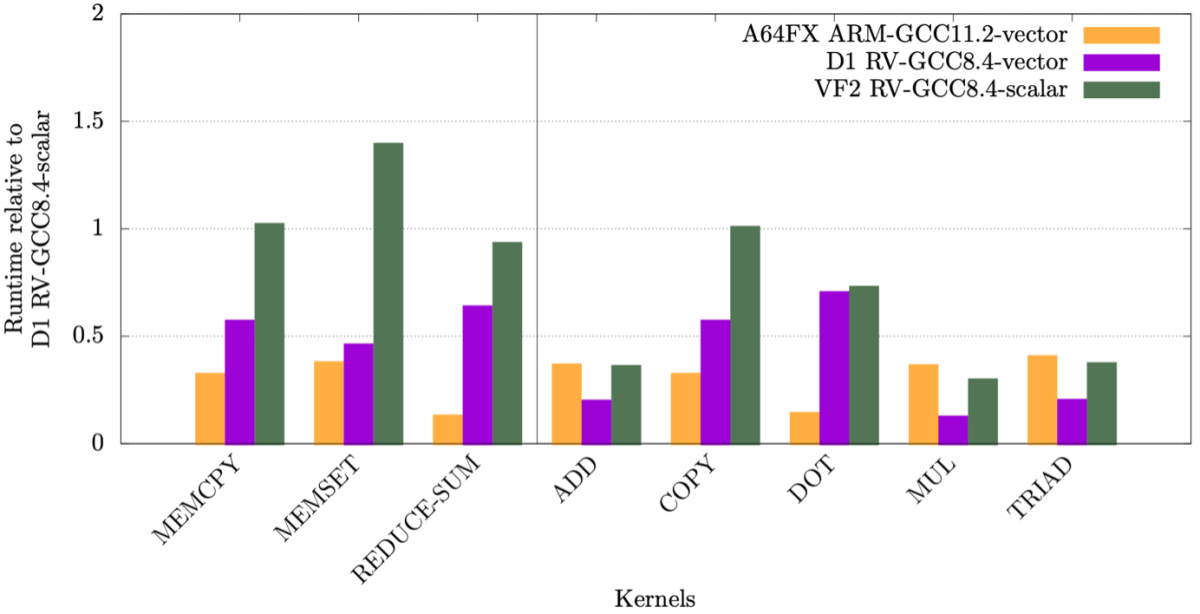

However, the fledgling nature of RISC-V ISA extensions has created some difficulties for developers. For example, the ‘V’ vector extension, commonly referred to as ‘RVV’, was frozen at version 1.0 in late September 2021. Whilst this was a great milestone, the fact that it is incompatible with previous RVV versions is unfortunate, as the only currently available hard RVV-enabled CPU, the C906, uses the incompatible v0.7 specification. Since both the GCC and LLVM / Clang compilers target frozen or ratified ISA extensions, in this case RVV v1.0, developers are unable to target the vector support provided by the D1 using mainline compiler versions and are forced to rely on the XuanTie-developed GCC v8.4. Unfortunately, this is no longer publicly available from the manufacturer but can be downloaded from the University of Edinburgh’s DataShare website [8]. When targeting C906 devices, such as the Allwinner D1, there are tangible runtime performance benefits to be gained by generating vectorised code using the XuanTieGCC compiler, as shown in Figure 3 for a number of the RAJAperf [9] benchmark kernels [10].

Figure 3: Relative runtime performance of vectorised RISC-V versus scalar code [10].

Another approach to leveraging the vectorisation support of the Allwinner D1, is to use the RVV v1.0 to v0.7 rollback tool [11], developed by Dr Joseph Lee as part of the ExCALIBUR H&ES RISC-V testbed project [12]. Here the mainline GCC and LLVM/Clang compilers can be used to autovectorise codes, with the tool translating the resultant RVV v1.0 assembly language ‘.s’ files to RVV v0.7 ‘.s’ source files. These are then assembled by the XuanTieGCC compiler to generate object ‘.o’ files / binaries for execution on the Allwinner D1-based boards.

Although this still requires the use the XuanTie GCC compiler, the original source code is compiled with up-to-date mainstream compiler versions. More information on using the RVV rollback tool and general information regarding the compilation of RISC-V vector codes can be found on the RISC-V testbed website [13].

More generally, the RISC-V testbed has been provided to support researchers who wish to test their codes on the currently available RISC-V hardware. At present, the testbed has 24 RISC-V cores available within a slurm cluster, with additional boards coming online during April and May 2023, bringing the total core count to 72. You can apply for access to the RISC-V testbed using the steps outlined on the website [14].

When we consider the original RISC architecture heyday in the late 1990s and early 2000s, and the current rise of the RISC-based ARM and RISC-V CPU architectures, it seems that Mark Twain was right.

[2] ‘MacBook Pro (Intel) vs MacBook Pro (M1 Pro/Max)’, Macworld. https://www.macworld.com/article/668176/macbook-pro-intel-vs-macbook-pr… (accessed Apr. 07, 2023).

[3] ‘November 2021 | TOP500’. https://www.top500.org/lists/top500/2021/11/ (accessed Apr. 07, 2023).

[4] ‘Overview of OpenSPARC Resources’. https://www.oracle.com/servers/technologies/opensparc-overview.html (accessed Apr. 07, 2023).

[5] ‘Specifications – RISC-V International’. https://riscv.org/technical/specifications/ (accessed Apr. 07, 2023).

[6] F. Embeddev, ‘RISC-V Instruction Set Manual, Volume I: RISC-V User-Level ISA’, Five EmbedDev. https://www.five-embeddev.com//riscv-isa-manual/latest/rv32e.html (accessed Apr. 07, 2023).

[7] R. Quinnell, ‘Creating a Custom Processor with RISC-V’, EE Times Europe, Mar. 29, 2019. https://www.eetimes.eu/creating-a-custom-processor-with-risc-v/ (accessed Apr. 07, 2023).

[8] J. Lee, ‘RISC-V GNU compiler toolchains with vector extension support’, Mar. 2023, doi: 10.7488/ds/3831.

[9] ‘LLNL/RAJAPerf’. Lawrence Livermore National Laboratory, Mar. 31, 2023. Accessed: Apr. 07, 2023. [Online]. Available: https://github.com/LLNL/RAJAPerf

[10] J. Lee, ‘Benchmarks update’, ExCALIBUR H&ES RISC-V testbed, Mar. 29, 2023. http://riscv.epcc.ed.ac.uk/success/benchmarks/ (accessed Apr. 07, 2023).

[11] J. Lee, ‘RISCVtestbed/rvv-rollback’. RISC-V testbed, Mar. 22, 2023. Accessed: Apr. 07, 2023. [Online]. Available: https://github.com/RISCVtestbed/rvv-rollback

[12] N. Brown, J. Lee, and M. Jamieson, ‘ExCALIBUR H&ES RISC-V testbed’, ExCALIBUR H&ES RISC-V testbed. http://riscv.epcc.ed.ac.uk/ (accessed Apr. 07, 2023).

[13] J. Lee, ‘Compiling Vector Code’, ExCALIBUR H&ES RISC-V testbed, Nov. 23, 2022. http://riscv.epcc.ed.ac.uk/issues/compiling-vector/ (accessed Apr. 07, 2023).

[14] N. Brown and J. Lee, ‘Applying for access’, ExCALIBUR H&ES RISC-V testbed, Apr. 05, 2023. http://riscv.epcc.ed.ac.uk/documentation/access/ (accessed Apr. 07, 2023).