Fortran High-Level Synthesis: reducing the barriers to accelerating HPC codes on FPGAs

31 October 2023

Computer programs were first written in Fortran back in the 1960s, when programmers had to undertake the difficult task of generating punch cards to run codes. The method used to write programs has evolved greatly since, but as EPCC PhD student Gabriel Rodriguez-Canal explains, Fortran is still as present as any other modern programming language.

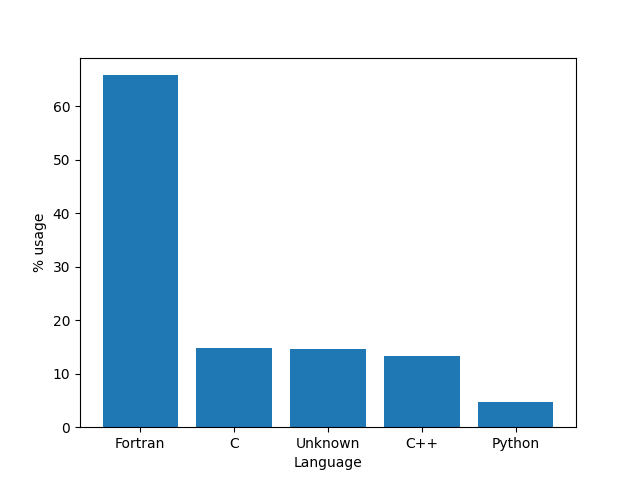

This is specially true in the field of supercomputing, where we have accumulated a large legacy scientific codebase over time. And scientists still develop in Fortran now, thanks to the powerful combination of expressiveness through its high level constructs that map very well to their mathematical equations and performance, since Fortran is a compiled language. In fact, over two thirds of the codes running on ARCHER2 in July 2023 were written in Fortran.

Figure 1: Percentage of time use of codes on ARCHER2.

Scaling codes

There is a growing interest in scaling up these codes: we want to run them faster or on bigger data sizes. We also want to do so while minimising the energy costs where possible.

HPC deals with this challenge in a variety of ways, one of the most successful and popular being the use of accelerators. In particular, FPGAs provide a very good compromise, achieving high performance by exploiting parallelism in the codes and energy efficiency. This is due to their reconfigurability, meaning their physical layout is not fixed upon manufacture, but defined by the programmer. This is possible thanks to the high-level synthesis (HLS) tools provided by the vendors, whereby the user writes high-level code that ultimately gets translated into hardware.

Although great at simplifying the hardware generation process, such tools have the major limitation that they only support C/C++, forcing Fortran programmers to translate their codes into C/C++ before even getting close to an FPGA. This is costly and error-prone, given the differences in array indexing in between both languages and the lack of support for subselections in C/C++.

Lowering the barrier to entry

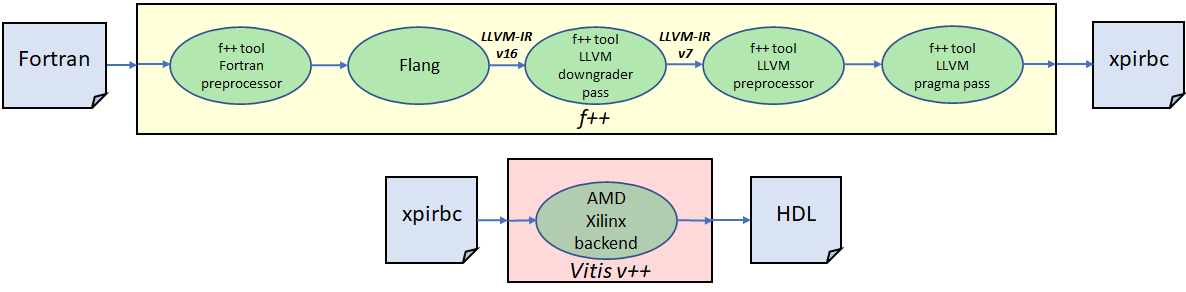

Fortran-HLS lowers the barrier to entry for FPGAs for Fortran users, enabling Fortran in the AMD Xilinx ecosystem, Vitis HLS. It does so by replacing the default C/C++ front-end, which takes care of transforming the input source code into a general language agnostic form called intermediate representation (IR), by LLVM Flang, the state-of-the-art Fortran front-end. This IR is fed to the Vitis HLS back-end, which deals with the generation of a hardware representation of the initial code.

Fortran-HLS acts on two ends:

- It adds awareness to Flang of the HLS constructs, so they can be added to the Fortran source code and processed by the front-end.

- It preprocesses the IR so the HLS constructs are conformant to the form expected by the back-end.

Figure 2: Flow of Fortran-HLS.

Conference presentations

This work was presented at FPL'23, the premier FPGA conference, with the title "Fortran High-Level Synthesis: Reducing the barriers to accelerating HPC codes on FPGAs". We demonstrated that our tool is capable of generating hardware for real-life codes with the same performance as the original toolchain based on C/C++. The research is promising, as not only does it enable Fortran on FPGAs but it provides a tool onto which any other LLVM-based frontend can be hooked. Thus, any tool that generates LLVM IR can generate hardware for AMD Xilinx FPGAs thanks to our tool.

We have already levaraged this feature in our work "Stencil-HMLS: A multi-layered approach to the automatic optimisation of stencil codes on FPGA", to be presented in the workshop H2RC at SC'23, where we carry out MLIR-based optimisation of stencil codes for FPGA and our tool discussed here is leveraged for hardware generation.

Paper

Fortran High-Level Synthesis: Reducing the barriers to accelerating HPC codes on FPGAs https://arxiv.org/pdf/2308.13274.pdf

Author

Gabriel Rodriguez-Canal, EPCC PhD student

Gabriel will attend SC23 as a Student Volunteer. Read more on our events page.