Representing HPC at the RISC-V North America Summit

25 November 2025

RISC-V is an open Instruction Set Architecture (ISA) standard. With over 20 billion RISC-V based CPUs manufactured since it was first proposed in 2010, the technology has grown phenomenally over the past 15 years.

However, for all its successes, RISC-V is yet to become mainstream in high performance computing (HPC), although we are seeing progress here year on year. For instance, EPCC hosts an HPC RISC-V testbed system that this year was certified by the standards body as an official ecosystem lab.

There are three RISC-V summits held each year: in Europe, North America and China. The North American summit is held is Santa Clara, in the heart of Silicon Valley. Running over three days, it is especially popular with local US technology companies who are using RISC-V heavily, as well as attracting a wider national and international audience.

RISC-V and HPC keynote talk

In my role as chair of the RISC-V HPC SIG, I gave a keynote at this year's US summit entitled 'Reimagining the Future of High Performance Computing Catalysed by RISC-V'. In it I reflected on the most important contributions that RISC-V can offer the HPC community, the current state of the art here, and a high level view of challenges that must be addressed to encourage adoption. This coincided with the release of the SIG's RISC-V for HPC gap analysis whitepaper, which is the first step in highlighting important parts of the RISC-V ecosystem that need to be addressed for HPC. Given the announcements and promises made by several RISC-V vendors about powerful CPUs in 2026, I predicted that next year could be a watershed moment for RISC-V in HPC.

Collaboration breakfast

The last day of the summit began early with a collaboration breakfast sponsored by Google. As a RISC-V ambassador, I was one of four panelists and the idea was to have a general discussion around some of the hottest topics in RISC-V. We explored the community side of RISC-V, where we as panelists see the major blockers (hardware availability was fairly ubiquitous!), how we can better encourage university courses to give students more exposure to RISC-V, and some aspects around the software ecosystem. It was a great discussion, with some very interesting points raised, and even though the hour was early the room was packed (although the free breakfast might have had something to do with it!)

Members' Day HPC discussions

The first day of the summit is for members only, where those who are members of RISC-V International (it's free for individuals and academic institutions to join) take a deeper dive into the technical side. There is also the opportunity to have in-person meetings.

I gave the talk "RISC-V and HPC: Recent successes, current challenges and future opportunities" on behalf of the HPC SIG. It provided a deep dive around SIG activities, how we have seen things progress in the past few years, and a call for the wider RISC-V community to help and contribute to key areas.

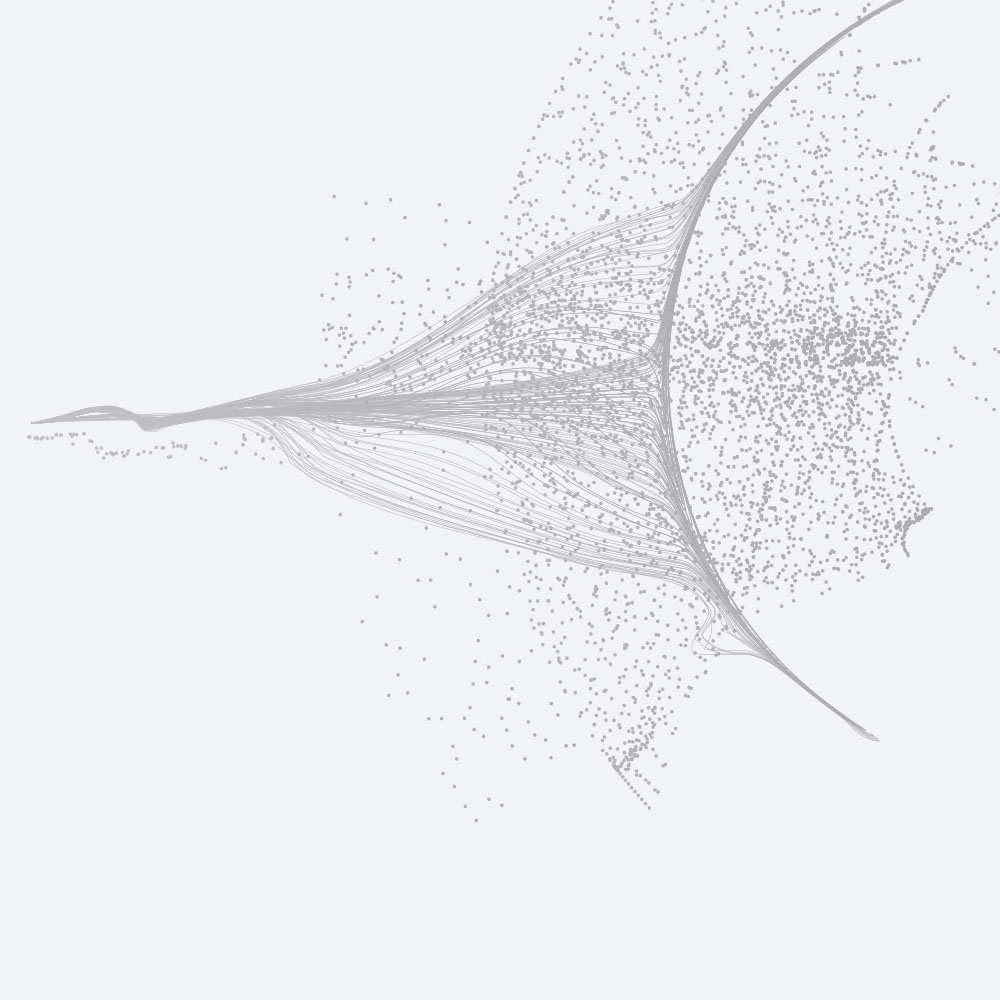

What struck me when writing this talk was the progress we have seen in papers submitted by the research community to our RISC-V for HPC workshop series. For each year (2023–2025), I highlighted the key themes across papers that the community was researching and working on, enabling us to identify patterns. My overall reflection here was that we are seeing growth and maturity building in RISC-V for HPC, certainly in some specific areas, and from this we can potentially identify where the community might grow in the future. My slides are available. See 'RISC-V and HPC: Recent successes, current challenges and future opportunities'.

I also chaired the in-person HPC SIG breakout session where around 40 of us got into a room and discussed some different things related to the SIG. This was an opportunity to raise some general topics and see what ideas and comments people had about them. In fact it was a really useful opportunity to hear from some RISC-V voices who are interested in HPC, but do not necessarily have time to join our SIG calls.

For example, we are currently undertaking the collection and curation of HPC benchmarks, with the idea being that vendors should consider measuring against them when developing their hardware as this is the sort of thing important to HPC. There was lots of discussion on this point, exploring what makes a good benchmarking suite and some of the potential pitfalls as well as the importance of setting realistic constraints and expections.

An HPC RISC-V demo on the show floor

The summit also includes an exhibition show floor, where vendors and other RISC-V organisations have booths highlighting their latest technologies. As part of this there is a demo zone, where attendees can play with the latest RISC-V hardware.

Previously I had ported EPCC's 'design a wing' demo to RISC-V, which enables people to design an aircraft wing and then simulate it, providing a real-time view of whether an aircraft with that wing would take off or not. This is always popular, and a strong illustration around the importance of simulation.

Many attendees experimented with designing a wing and we simulated it on a SiFive Quad-Core P550 board. Most importantly for me, this demonstrates that all the underlying HPC technologies such as MPI, OpenMP, and Fortran are well supported on RISC-V and usable by the HPC community.

In summary

It was a busy few days in Santa Clara, but it was always hugely motivating to see the energy in and around RISC-V and the wide range of people and organisations who are leveraging the standard. I see the RISC-V community and associated technologies are growing rapidly year on year, and all the different activities at the US Summit really demonstrated that. I can't wait to see what 2026 has in store!