Review: the Second International RISC-V for HPC workshop

28 November 2023

EPCC's Nick Brown writes about the recent Second International RISC-V for HPC workshop, which was held at SC23 in Denver, Colorado this month.

RISC-V is an open and community led Instruction Set Architecture (ISA) standard which can then be used as a basis for developing CPU implementations. By conforming to this common standard, such CPUs then enjoy a wealth of existing, compatible, software and tooling. Since it was first proposed over a decade ago, there have been many CPUs based upon RISC-V, with developers ranging from large multi-national corporations to individuals. Indeed, Qualcomm recently announced that it has shipped over a billion RISC-V powered devices (see this post on X, formerly Twitter).

There is great potential for RISC-V to significantly enhance HPC. The purpose of this workshop was to explore the challenges and opportunities around adopting RISC-V for HPC workloads. As SC is the world's leading HPC conference, it was a great opportunity to help connect the RISC-V and HPC worlds, explore current activities, and help drive growth of RISC-V in HPC. The organisation of the workshop was led by myself as part of the ExCALIBUR H&ES RISC-V testbed in collaboration with the RISC-V HPC SIG.

Invited talk by RISC-V International CTO

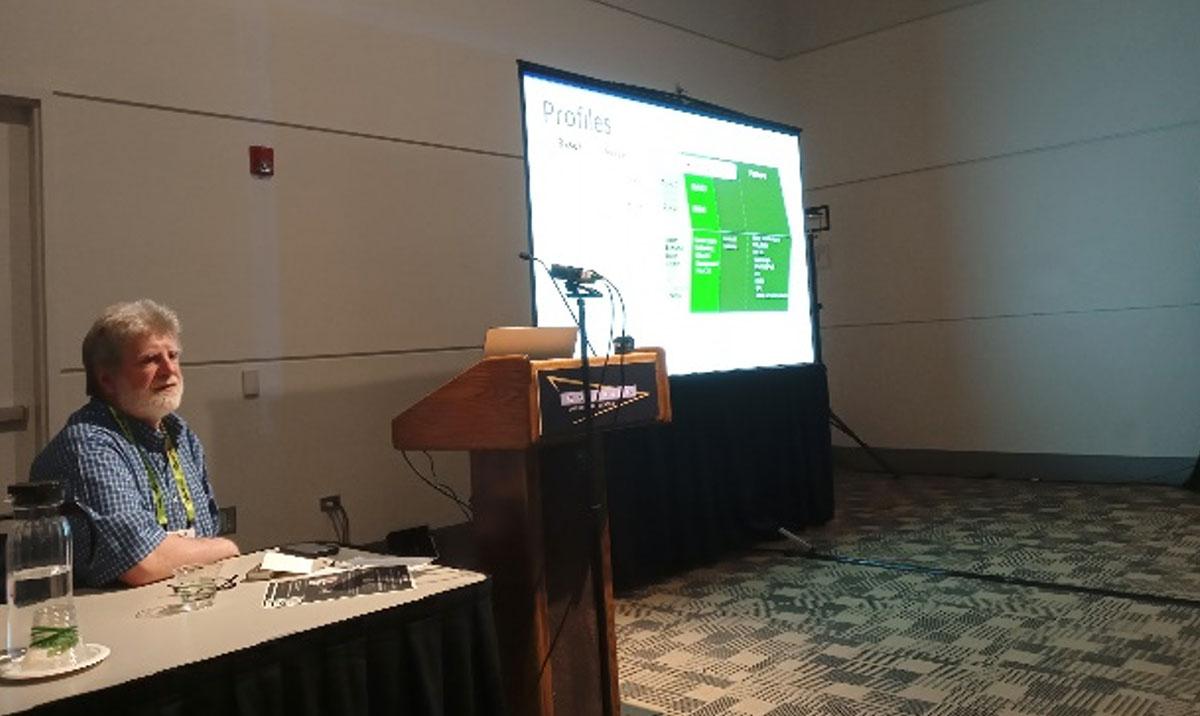

The RISC-V for HPC workshop was a great success, with a completely full room. It began with an invited talk by Mark Himelstein, the Chief Technology Officer (CTO) of RISC-V International, the body responsible for overseeing RISC-V.

Mark described the history of RISC-V, some recent developments, and key proposals that are in the pipeline which are of importance to the HPC community. Mark is a very engaging speaker, with a wealth of knowledge not only of RISC-V but also computing more generally. Little wonder then that his talk was followed by an active discussion with the audience, with Mark fielding numerous questions about RISC-V in general and his views around standardisation. The room allocated for the workshop was filled to capacity for Mark’s talk, and people were queuing outside to be allowed in by the fire marshal, not only demonstrating the interest in RISC-V from the HPC community but also being a hugely successful start to the workshop.

Mark Himelstein, CTO of RISC-V International, delivering the workshop invited talk on the current state of RISC-V and future opportunities

Vendor lightning talks

The workshop then continued with vendor lightning talks, where Esperanto Technologies, SOPHGO, Inspire Semiconductor, and E4 Computer Engineering gave brief presentations about their hardware products.

I was keen for us to have this as a session in the workshop to demonstrate that there are real-world HPC hardware products being built around RISC-V that can be used by the community today. For instance, Esperanto Technologies described a 80,000 core RISC-V system based on its 1088 RISC-V core CPU. This was followed by SOPHGO describing the SG2042 64-core high performance commodity RISC-V CPU and its immediate roadmap, and Inspire Semiconductor introducing its circa 1600 core RISC-V accelerator board.

Research papers

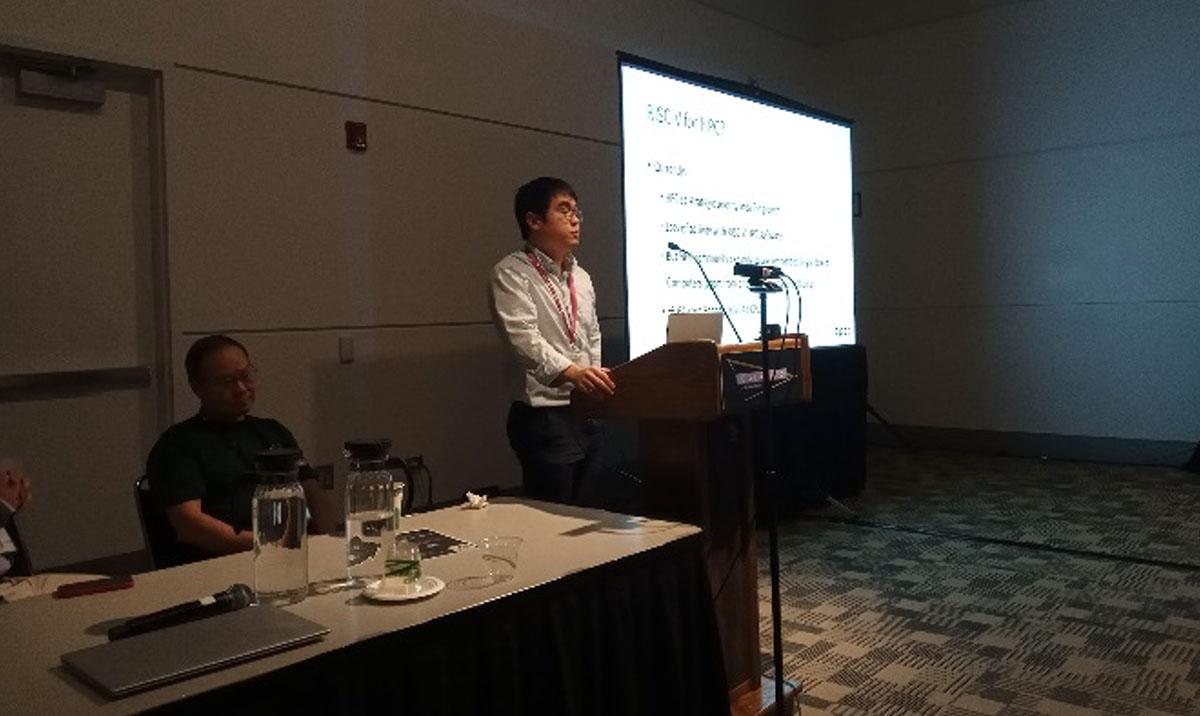

After the vendor talks, research papers on RISC-V for HPC were presented. These included application studies, benchmarking RISC-V HPC hardware, and exploring algorithms tuned specifically to the nature of the ISA. EPCC’s Joseph Lee presented work we have done in EPCC around benchmarking the SG2042 (see the preprint of the paper).

There was good audience interaction throughout, with many questions asked and discussion points raised. The research papers have been published in the ACM SC workshop proceedings.

EPCC's Joseph Lee presenting work done at EPCC on benchmarking the 64-core SG2042 RISC-V CPU.

The workshop was a great success. Not only was the room packed to capacity with people queuing to be allowed in, but HPCWire wrote an article reporting the latest news in RISC-V based upon presentations at the workshop.

Next international RISC-V workshop

On the back of this event we are now planning the Third International Workshop on RISC-V for HPC which will be in collaboration with HPC Asia on the 25th of January 2024 in Nagoya, Japan. This will be an opportunity to share RISC-V activities with the Asian HPC community, and a call for papers is currently open until the 28th of November with more details on the workshop website.